ZHCSBL7 - AUGUST 2013

www.ti.com.cn

# 高性能 12A 单通道同步降压转换器

# 特性

- 宽转换输入电压范围: 1.5V 至 22V

- 宽 VDD 输入电压: 4.5V 至 25V

- 输出电压范围: 0.6V 至 5.5V

- 带有 12A 持续输出电流的集成型功率金属氧化物半导体场效应晶体管 (MOSFET)

- 支持所有陶瓷输出电容器

- 基准电压 600mV (耐受幅度 ±0.5%)

- 内置 5V 低压降稳压器 (LDO)

- D-CAP3™ 100ns 负载阶跃响应模式

- 自动跳跃 Eco-mode™ 用于轻负载有效性

- 针对严格输出纹波和电压要求的连续传导模式 (FCCM)

- 具有八个可选择频率设置的自适应接通时间控制架构

- 热关断

- 预充电启动功能

- 内置输出放电

- 开漏电源正常输出

- 集成升压开关

- 内置保护:过压、欠压、过流

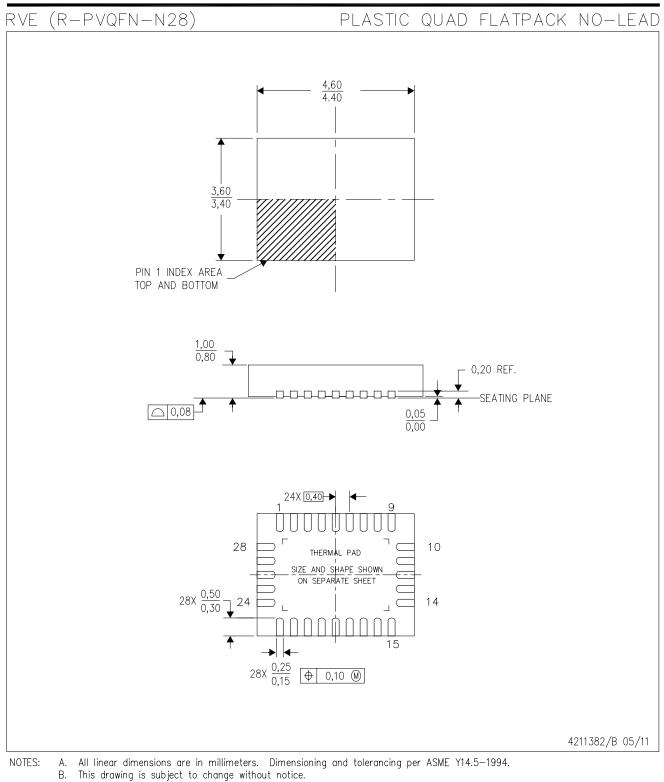

- 3.5mm × 4.5mm 28 引脚四方扁平无引线 (QFN) 封装

# 应用范围

- 服务器和云计算负载点 (POL)

- I/O 电源

- 打印机

- 电信类

# 说明

**TPS53515** 是一款具有自适应接通时间 **D-CAP3** 模式 控制的小尺寸、单通道降压转换器。此器件为空间有 限的电源系统提供易于使用且低外部组件数量。

这个器件特有高性能集成 MOSFET,精准 0.5% 0.6V 基准和集成的升压开关。 竞争优势包括极低外部组件 数量、快速负载瞬态响应、自动跳跃模式运行、内部软 启动控制,并且无需补偿。

转换输入电压范围介于 1.5V 至 22V 之间。 VDD 输入 电压的范围介于 4.5V 至 25V 之间。输出电压范围为 0.6V 至 5.5V。TPS53515 采用 28 引脚 QFN 封装, 额定温度范围介于 -40℃ 至 +85℃ 之间。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. D-CAP3, Eco-mode are trademarks of Texas Instruments.

### ZHCSBL7 -AUGUST 2013

www.ti.com.cn

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                    |                          |                   | VALUE |                                                                                                                                                                                                                                                        | UNIT |

|------------------------------------|--------------------------|-------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                    |                          |                   | MIN   | MAX                                                                                                                                                                                                                                                    |      |

|                                    | EN                       |                   | -0.3  | 7.7                                                                                                                                                                                                                                                    |      |

| Input voltage range <sup>(2)</sup> | 0.14/                    | DC                | -3    | 30                                                                                                                                                                                                                                                     | V    |

|                                    | SW                       | Transient < 10 nS | -5    | 32                                                                                                                                                                                                                                                     |      |

|                                    | VBST                     |                   | -0.3  | 36                                                                                                                                                                                                                                                     |      |

|                                    | VBST <sup>(3)</sup>      |                   | -0.3  | 6                                                                                                                                                                                                                                                      |      |

|                                    | VBST when                | transient < 10 nS |       | 38                                                                                                                                                                                                                                                     |      |

|                                    | VDD                      |                   | -0.3  | 28                                                                                                                                                                                                                                                     |      |

|                                    | VIN                      |                   | -0.3  | 30                                                                                                                                                                                                                                                     |      |

|                                    | VDD                      | -0.3              | 6     |                                                                                                                                                                                                                                                        |      |

|                                    | PGOOD                    |                   | -0.3  | 7.7                                                                                                                                                                                                                                                    |      |

| Output voltage range               | VREG, TRIF               | 2                 | -0.3  | 6                                                                                                                                                                                                                                                      | v    |

| Tanananatuna                       | Junction, T <sub>J</sub> |                   | -40   | $\begin{array}{c cccc} -0.3 & 7.7 \\ \hline -3 & 30 \\ \hline -5 & 32 \\ \hline -0.3 & 36 \\ \hline -0.3 & 6 \\ \hline \\ -0.3 & 28 \\ \hline -0.3 & 30 \\ \hline \\ -0.3 & 30 \\ \hline \\ -0.3 & 7.7 \\ \hline \\ -0.3 & 6 \\ \end{array} \lor \lor$ |      |

| Temperature                        | Storage, T <sub>st</sub> | 9                 | -55   | 150                                                                                                                                                                                                                                                    | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) Voltage values are with respect to the SW terminal.

# THERMAL INFORMATION

|                         |                                                             | TPS53515 |       |

|-------------------------|-------------------------------------------------------------|----------|-------|

|                         | THERMAL METRIC <sup>(1)</sup>                               | RVE      | UNITS |

|                         |                                                             | 28 PINS  |       |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 37.5     |       |

| $\theta_{JCtop}$        | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 34.1     |       |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup>         | 18.1     | 80 AA |

| Ψ <sub>JT</sub>         | Junction-to-top characterization parameter <sup>(5)</sup>   | 1.8      | °C/W  |

| $\Psi_{JB}$             | Junction-to-board characterization parameter <sup>(6)</sup> | 18.1     |       |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 2.2      |       |

(1) 有关传统和全新热度量的更多信息,请参阅 *IC 封装热度量* 应用报告 (文献号:ZHCA543)。

(2) 在 JESD51-2a 描述的环境中,按照 JESD51-7 的规定,在一个 JEDEC 标准高 K 电路板上进行仿真,从而获得自然对流条件下的结至环 境热阻抗。

(3) 通过在封装顶部模拟一个冷板测试来获得结至芯片外壳(顶部)的热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到内容接近的说明。

(4) 按照 JESD51-8 中的说明,通过在配有用于控制 PCB 温度的环形冷板夹具的环境中进行仿真,以获得结至电路板的热阻。

(5) 结至顶部的特征参数,(ψ<sub>JT</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第6章和第7章)中描述的程序从仿真数据中提取出该参数以便获得 θ<sub>JA</sub>。

(6) 结至电路板的特征参数,(ψ<sub>JB</sub>),估算真实系统中器件的结温,并使用 JESD51-2a(第6章和第7章)中描述的程序从仿真数据中提取出该 参数以便获得 θ<sub>JA</sub>。

(7) 通过在外露(电源)焊盘上进行冷板测试仿真来获得结至芯片外壳(底部)热阻。 不存在特定的 JEDEC 标准测试,但可在 ANSI SEMI 标准 G30-88 中找到了内容接近的说明。

# **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                      |                                | MIN  | MAX | UNIT |

|----------------------|--------------------------------|------|-----|------|

|                      | EN                             | -0.1 | 7   |      |

| Input voltage range  | SW                             | -3   | 27  |      |

|                      | VBST                           | -0.1 | 28  |      |

|                      | VBST <sup>(1)</sup>            | -0.1 | 5.5 | V    |

|                      | VDD                            | 4.5  | 25  |      |

|                      | VIN                            | 1.5  | 18  |      |

|                      | VO, FB, MODE, RF               | -0.1 | 5.5 |      |

| Output voltage range | PGOOD                          | -0.1 | 7   | V    |

|                      | VREG, TRIP                     | -0.1 | 5.5 | v    |

| T <sub>A</sub>       | Operating free-air temperature | -40  | 85  | °C   |

(1) Voltage values are with respect to the SW pin.

# **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range, VREG = 5 V, EN = 5 V (unless otherwise noted)

|                            | PARAMETER                                                                         | TEST CONDITIONS                                                          | MIN   | TYP  | MAX                                     | UNIT |

|----------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------|------|-----------------------------------------|------|

| SUPPLY                     | CURRENT                                                                           |                                                                          |       |      |                                         |      |

| I <sub>VDD</sub>           | VDD bias current                                                                  | $T_A = 25^{\circ}C$ , No load<br>Power conversion enabled (no switching) |       | 1350 | 1850                                    | μA   |

| I <sub>VDDSTBY</sub>       | VDD standby current                                                               | $T_A = 25^{\circ}C$ , No load<br>Power conversion disabled               |       | 850  | 1150                                    | μA   |

| I <sub>VIN(leak)</sub>     | VIN leakage current                                                               | $V_{EN} = 0 V$                                                           |       |      | 0.5                                     | μA   |

| VREF OU                    | TPUT                                                                              |                                                                          |       |      |                                         |      |

| V <sub>VREF</sub>          | Reference voltage                                                                 | FB w/r/t GND, $T_A = 25^{\circ}C$                                        | 597   | 600  | 603                                     | mV   |

| M                          | Deference voltage teleronee                                                       | FB w/r/t GND, $T_J = 0^{\circ}C$ to $85^{\circ}C$                        | -0.7% |      | 1.0%                                    |      |

| V <sub>VREFTOL</sub>       | FTOL       Reference voltage tolerance         PUT VOLTAGE       FB input current | FB w/r/t GND, $T_J = -40^{\circ}$ C to $85^{\circ}$ C                    | -1%   |      | 1%                                      |      |

| OUTPUT                     | VOLTAGE                                                                           | · · · · · · · · · · · · · · · · · · ·                                    |       |      |                                         |      |

| I <sub>FB</sub>            | FB input current                                                                  | V <sub>FB</sub> = 600 mV                                                 |       | 50   | 100                                     | nA   |

| VODIS VO discharge current |                                                                                   | $V_{VO}$ = 0.5 V, Power Conversion Disabled                              | 10    | 12   | 15                                      | mA   |

| SMPS FR                    | EQUENCY                                                                           |                                                                          |       |      |                                         |      |

|                            |                                                                                   | $V_{IN}$ = 12 V, $V_{VO}$ = 3.3 V, $R_{DR}$ < 0.041                      |       | 250  |                                         |      |

|                            |                                                                                   | $V_{IN}$ = 12 V, $V_{VO}$ = 3.3 V, $R_{DR}$ = 0.096                      | 300   |      |                                         |      |

|                            |                                                                                   | $V_{IN} = 12 \text{ V}, V_{VO} = 3.3 \text{ V}, R_{DR} = 0.16$           |       | 400  |                                         |      |

| 4                          | (0, 1)                                                                            | V <sub>IN</sub> = 12 V, V <sub>VO</sub> = 3.3 V, R <sub>DR</sub> = 0.229 |       | 500  |                                         |      |

| f <sub>SW</sub>            | VO switching frequency <sup>(1)</sup>                                             | $V_{IN}$ = 12 V, $V_{VO}$ = 3.3 V, $R_{DR}$ = 0.297                      |       | 600  | 1150<br>0.5<br>603<br>1.0%<br>1%<br>100 | kHz  |

|                            |                                                                                   | $V_{IN}$ = 12 V, $V_{VO}$ = 3.3 V, $R_{DR}$ = 0.375                      |       | 750  |                                         |      |

|                            |                                                                                   | $V_{IN}$ = 12 V, $V_{VO}$ = 3.3 V, $R_{DR}$ = 0.461                      |       | 850  |                                         |      |

|                            |                                                                                   | V <sub>IN</sub> = 12 V, V <sub>VO</sub> = 3.3 V, R <sub>DR</sub> > 0.557 |       | 1000 |                                         |      |

| t <sub>ON(min)</sub>       | Minimum on-time                                                                   |                                                                          |       | 60   |                                         | ns   |

| t <sub>OFF(min)</sub>      | Minimum off-time                                                                  | $T_A = 25^{\circ}C$                                                      | 175   | 240  | 310                                     | ns   |

| INTERNA                    | L BOOTSTRAP SW                                                                    |                                                                          | ;     |      |                                         |      |

| V <sub>F</sub>             | Forward Voltage                                                                   | $V_{VREG-VBST}$ , $T_A = 25^{\circ}C$ , $I_F = 10 \text{ mA}$            |       | 0.15 | 0.25                                    | V    |

| I <sub>VBST</sub>          | VBST leakage current                                                              | T <sub>A</sub> = 25°C, V <sub>VBST</sub> = 33 V, V <sub>SW</sub> = 28 V  |       | 0.01 | 1.5                                     | μA   |

Resistor divider ratio ( $R_{DR}$ ) is described in Equation 1. Specified by design. Not production tested. (1)

(2)

ZHCSBL7 -AUGUST 2013

Texas **NSTRUMENTS**

www.ti.com.cn

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range, VREG = 5 V, EN = 5 V (unless otherwise noted)

|                                               | PARAMETER                                                                | TEST CONDITIONS                                                              | MIN   | TYP   | MAX  | UNI  |  |

|-----------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|-------|------|------|--|

|                                               | RESHOLD                                                                  |                                                                              | 1     |       |      |      |  |

| V <sub>ENH</sub>                              | EN enable threshold voltage                                              |                                                                              | 1.3   | 1.4   | 1.5  | V    |  |

| V <sub>ENL</sub>                              | EN disable threshold voltage                                             |                                                                              | 1.1   | 1.2   | 1.3  | V    |  |

| V <sub>ENHYST</sub>                           | EN hysteresis voltage                                                    |                                                                              |       | 0.22  |      | V    |  |

| V <sub>ENLEAK</sub>                           | EN input leakage current                                                 |                                                                              | -1    | 0     | 1    | μA   |  |

| SOFT STA                                      | RT                                                                       |                                                                              | 1     |       |      |      |  |

| t <sub>SS</sub>                               | Soft-start time <sup>(3)</sup>                                           |                                                                              |       | 1     |      | ms   |  |

| PGOOD CO                                      | OMPARATOR                                                                |                                                                              | 1     |       |      |      |  |

|                                               |                                                                          | PGOOD in from higher                                                         | 104%  | 108%  | 111% |      |  |

| .,                                            |                                                                          | PGOOD in from lower                                                          | 89%   | 92%   | 96%  |      |  |

| V <sub>PGTH</sub>                             | VDDQ PGOOD threshold                                                     | PGOOD out to higher                                                          | 113%  | 116%  | 120% |      |  |

|                                               | PGOOD sink current PGOOD delay time PGOOD leakage current RENT DETECTION | PGOOD out to lower                                                           | 80%   | 84%   | 87%  |      |  |

| I <sub>PG</sub>                               | PGOOD sink current                                                       | V <sub>PGOOD</sub> = 0.5 V                                                   | 4     | 6     |      | mA   |  |

|                                               |                                                                          | Delay tolerance for PGOOD going in                                           | -20%  |       | 20%  |      |  |

| t <sub>PGDLY</sub>                            | PGOOD delay time                                                         | Delay for PGOOD coming out                                                   |       | 2     |      | μs   |  |

| I <sub>PGLK</sub>                             | PGOOD leakage current                                                    | V <sub>PGOOD</sub> = 5 V                                                     | -1    | 0     | 1    | μA   |  |

|                                               |                                                                          | 1                                                                            |       |       |      |      |  |

| R <sub>TRIP</sub>                             | TRIP pin resistance range                                                |                                                                              | 20    |       | 70   | kΩ   |  |

|                                               |                                                                          | R <sub>TRIP</sub> = 52.3 kΩ                                                  | 10.1  | 12.0  | 13.9 | _    |  |

| 002                                           | Current limit threshold, valley                                          | $R_{\text{TRIP}} = 38 \text{ k}\Omega$                                       | 7.2   | 9.1   | 11.0 | A    |  |

|                                               | Negative current limit threshold,                                        | $R_{TRIP} = 52.3 \text{ k}\Omega$                                            | -15.3 | -11.9 | -8.5 |      |  |

| I <sub>OCLN</sub>                             | valley                                                                   | $R_{\text{TRIP}} = 38 \text{ k}\Omega$                                       | -12   | -9    | -6   | -6 A |  |

| V <sub>ZC</sub>                               | Zero cross detection offset                                              |                                                                              |       | 0     |      | mV   |  |

| PROTECTI                                      | ONS                                                                      |                                                                              |       |       |      |      |  |

|                                               | VREG undervoltage-lockout                                                | Wake-up                                                                      | 3.25  | 3.34  | 3.41 |      |  |

| V <sub>VREGUVLO</sub>                         |                                                                          | Shutdown                                                                     | 3.05  | 3.12  | 3.19 | V    |  |

|                                               | VREG undervoltage-lockout<br>(UVLO) threshold voltage                    | Wake-up (default)                                                            | 4.2   | 4.3   | 4.4  |      |  |

| V <sub>VDDUVLO</sub>                          | VDD UVLO threshold voltage                                               | Shutdown                                                                     | 4     | 4.03  | 4.16 | V    |  |

| V <sub>OVP</sub>                              | Overvoltage-protection (OVP) threshold voltage                           | OVP detect voltage                                                           | 116%  | 120%  | 124% |      |  |

| t <sub>OVPDLY</sub>                           | OVP propagation delay                                                    | With 100-mV overdrive                                                        |       | 300   |      | ns   |  |

| V <sub>UVP</sub>                              | Undervoltage-protection (UVP) threshold voltage                          | UVP detect voltage                                                           | 64%   | 68%   | 71%  |      |  |

| t <sub>UVPDLY</sub>                           | UVP delay                                                                | UVP filter delay                                                             |       | 1     |      | ms   |  |

| THERMAL                                       | SHUTDOWN                                                                 |                                                                              |       |       |      |      |  |

|                                               | Thermal chutdows thread at 4                                             | Shutdown temperature                                                         |       | 140   |      | •••  |  |

| SDN Thermal shutdown threshold <sup>(4)</sup> |                                                                          | Hysteresis                                                                   |       | 40    |      | °C   |  |

|                                               | AGE                                                                      |                                                                              |       |       |      |      |  |

| V <sub>REG</sub>                              | LDO output voltage                                                       | V <sub>IN</sub> = 12 V, I <sub>LOAD</sub> = 10 mA                            | 4.65  | 5     | 5.45 | V    |  |

| V <sub>DOVREG</sub>                           | LDO low droop drop-out voltage                                           | $V_{IN} = 4.5 \text{ V}, I_{LOAD} = 30 \text{ mA}, T_A = 25^{\circ}\text{C}$ |       |       | 365  | m∖   |  |

| ILDOMAX                                       | LDO over-current limit                                                   | $V_{IN} = 12 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                  | 170   | 200   |      | mA   |  |

|                                               | MOSFETS                                                                  |                                                                              | 1     |       | I    |      |  |

| R <sub>DS(on)H</sub>                          | High-side MOSFET on-resistance                                           |                                                                              |       | 13.8  | 18   | mΩ   |  |

| R <sub>DS(on)L</sub>                          | Low-side MOSFET on-resistance                                            |                                                                              |       | 5.9   | 8    | mΩ   |  |

# **DEVICE INFORMATION**

### **PIN DESCRIPTIONS**

| PIN   |     | I/O <sup>(1)</sup> |                                                                                                                                                                                                                                                            |  |  |  |  |  |

|-------|-----|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME  | NO. | 1/0(.)             | DESCRIPTION                                                                                                                                                                                                                                                |  |  |  |  |  |

| EN    | 3   | I                  | The enable pin turns on the DC-DC switching converter.                                                                                                                                                                                                     |  |  |  |  |  |

| FB    | 23  | I                  | V <sub>OUT</sub> feedback input. Connect this pin to a resistor divider between the VOUT pin and GND.                                                                                                                                                      |  |  |  |  |  |

| GND   | 22  | G                  | This pin is the ground of internal analog circuitry and driver circuitry. Connect GND to the PGND plane with a short trace (For example, connect this pin to the thermal pad with a single trace and connect the thermal pad to PGND pins and PGND plane). |  |  |  |  |  |

| GND1  | 27  | G                  | Connect this pin to ground. GND1 is the input of unused internal circuitry and must connect to ground.                                                                                                                                                     |  |  |  |  |  |

| GND2  | 28  | G                  | Connect this pin to ground. GND2 is the input of unused internal circuitry and must connect to ground.                                                                                                                                                     |  |  |  |  |  |

| MODE  | 21  | I                  | The MODE pin sets the forced continuous-conduction mode (FCCM) or Skip-mode operation. It also selects the ramp coefficient of D-CAP3 mode.                                                                                                                |  |  |  |  |  |

| NO    | 5   |                    | Net connected. These size are flection intervally.                                                                                                                                                                                                         |  |  |  |  |  |

| NC    | 18  |                    | Not connected. These pins are floating internally.                                                                                                                                                                                                         |  |  |  |  |  |

| DNC   | 26  | 0                  | Do not connect. This pin is the output of unused internal circuitry and must be floating.                                                                                                                                                                  |  |  |  |  |  |

|       | 10  |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       | 11  |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PGND  | 12  | G                  | These ground pins are connected to the return of the internal low-side MOSFET.                                                                                                                                                                             |  |  |  |  |  |

|       | 13  |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

|       | 14  |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PGOOD | 2   | 0                  | Open-drain power-good status signal which provides startup delay after the FB voltage falls within the specified limits. After the FB voltage moves outside the specified limits, PGOOD goes low within 2 µs.                                              |  |  |  |  |  |

| RF    | 1   | I                  | RF is the SW-frequency configuration pin. Connect this pin to a resistor divider between VREG and GND to program different SW frequency settings.                                                                                                          |  |  |  |  |  |

|       | 6   |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 0.44  | 7   |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

| SW    | 8   | B                  | SW is the output switching terminal of the power converter. Connect this pin to the output inductor.                                                                                                                                                       |  |  |  |  |  |

|       | 9   |                    |                                                                                                                                                                                                                                                            |  |  |  |  |  |

#### (1) I = Input, O = Output, B = Bidirectional, P = Supply, G = Ground

# TEXAS INSTRUMENTS

www.ti.com.cn

#### ZHCSBL7 -AUGUST 2013

# PIN DESCRIPTIONS (continued)

|        | PIN                                                                                                                                                                                                                                                   |             | DESCRIPTION                                                                                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | Image: No.     I/O <sup>(1)</sup> DESCRIPTION       Description     TRIP is the OCL detection threes sourced and sets the OCL trip v detailed OCP setting.       T     4     P     VBST is the supply rail for the h from this pin to the SW node. In | DESCRIPTION |                                                                                                                                                                                                                                         |

| TRIP   | 25                                                                                                                                                                                                                                                    | I/O         | TRIP is the OCL detection threshold setting pin. $I_{TRIP} = 10 \ \mu A$ at room temp, 3000 ppm/°C current is sourced and sets the OCL trip voltage. See the Current Sense and Overcurrent Protection section for detailed OCP setting. |

| VBST 4 |                                                                                                                                                                                                                                                       | Р           | VBST is the supply rail for the high-side gate driver (boost terminal). Connect the bootstrap capacitor from this pin to the SW node. Internally connected to VREG via bootstrap PMOS switch.                                           |

| VDD    | 19                                                                                                                                                                                                                                                    | Р           | Power-supply input pin for controller. Input of the VREG LDO. The input range is from 4.5 to 25 V.                                                                                                                                      |

|        | 15                                                                                                                                                                                                                                                    |             |                                                                                                                                                                                                                                         |

| VIN    | 16                                                                                                                                                                                                                                                    | Р           | VIN is the conversion power-supply input pins.                                                                                                                                                                                          |

|        | 17                                                                                                                                                                                                                                                    |             |                                                                                                                                                                                                                                         |

| VREG   | 20                                                                                                                                                                                                                                                    | 0           | VREG is the 5-V LDO output. This voltage supplies the internal circuitry and gate driver.                                                                                                                                               |

| VO     | 24                                                                                                                                                                                                                                                    | I           | VOUT voltage input to the controller.                                                                                                                                                                                                   |

ZHCSBL7 - AUGUST 2013

www.ti.com.cn

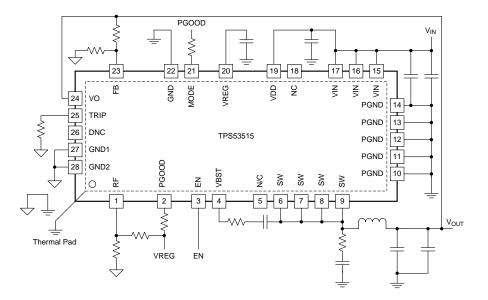

# **BLOCK DIAGRAM**

### ZHCSBL7 -AUGUST 2013

www.ti.com.cn

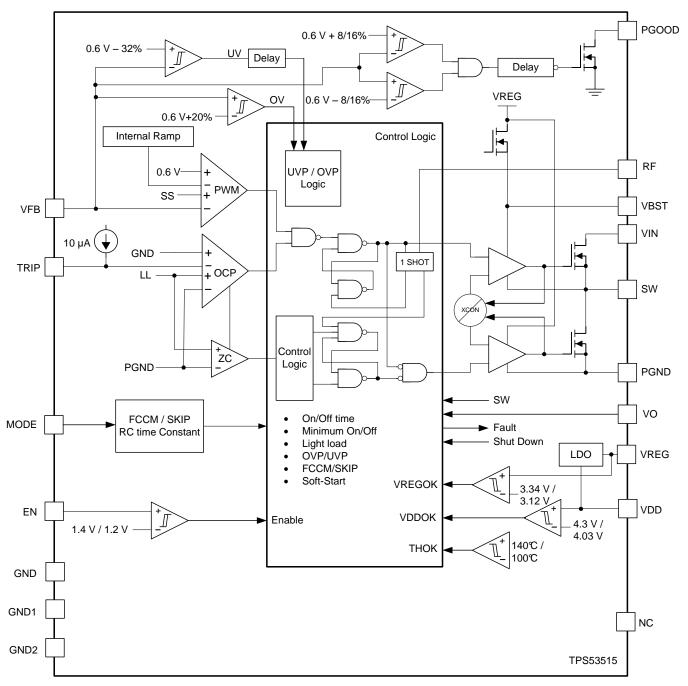

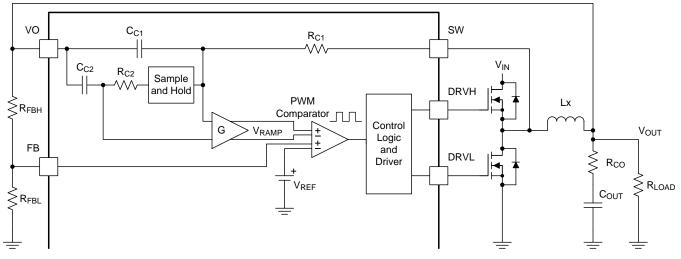

# **APPLICATION CIRCUIT DIAGRAM**

Figure 1. Typical Application Circuit Diagram

ZHCSBL7 -AUGUST 2013

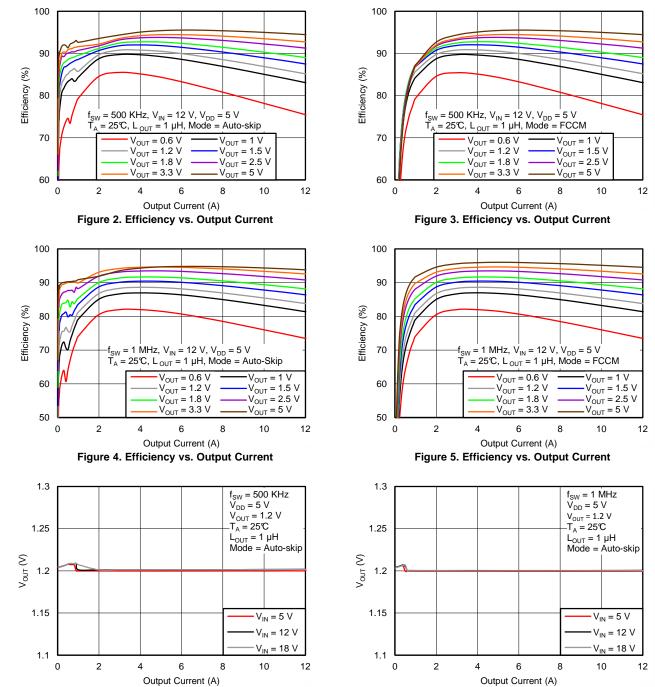

# **TYPICAL CHARACTERISTICS**

# ZHCSBL7 -AUGUST 2013

NSTRUMENTS

**FEXAS**

www.ti.com.cn

ZHCSBL7 - AUGUST 2013

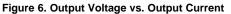

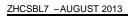

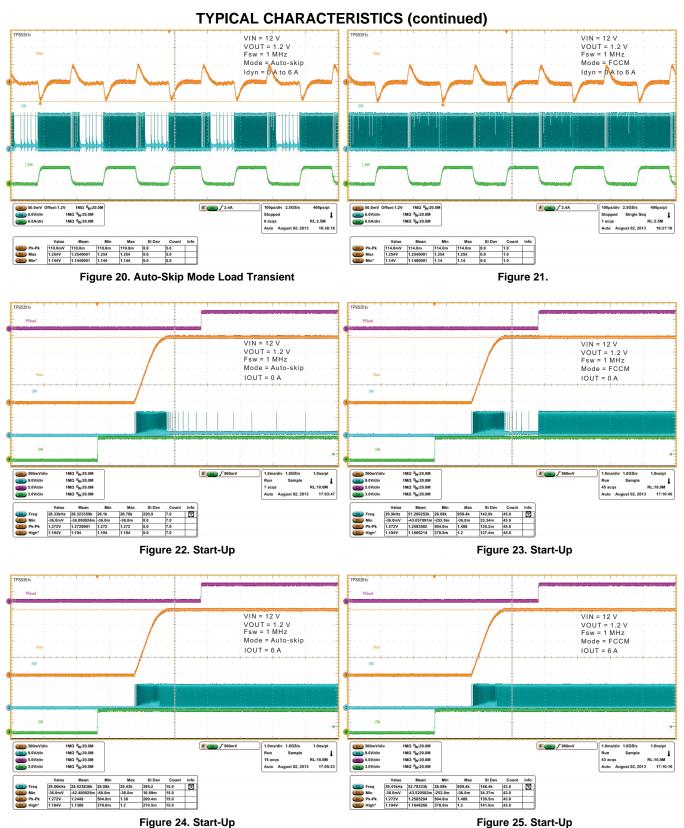

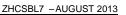

**TYPICAL CHARACTERISTICS (continued)**

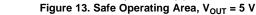

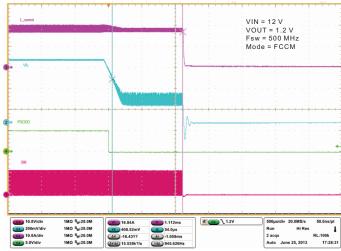

Figure 14. Auto-Skip Steady-State Operation

Figure 15. FCCM Steady-State Operation

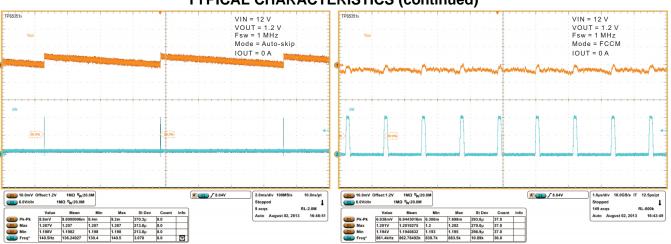

Figure 16. Auto-Skip Steady-State Operation

Figure 17. FCCM Steady-State Operation

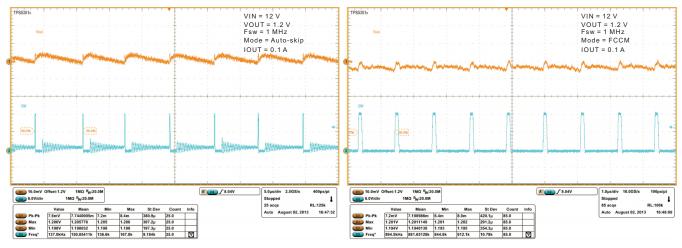

Figure 18. Auto-Skip Steady-State Operation

Figure 19. FCCM Steady-State Operation

INSTRUMENTS

www.ti.com.cn

TEXAS

# TPS53515

Figure 30. Pre-Bias Operation

Figure 31. Overvoltage Protection

#### ZHCSBL7 -AUGUST 2013

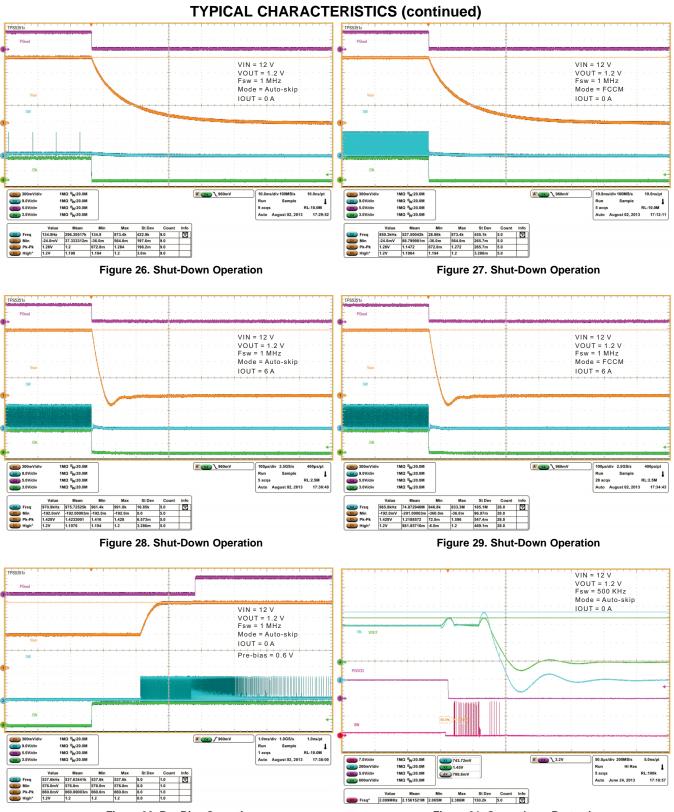

# **TYPICAL CHARACTERISTICS (continued)**

Figure 32. Overcurrent Protection

# **APPLICATION INFORMATION**

# **General Description**

The TPS53515 is a high-efficiency, single-channel, synchronous-buck converter. The device suits low-output voltage point-of-load applications with 12-A or lower output current in computing and similar digital consumer applications. The TPS53515 features proprietary D-CAP3 mode control combined with adaptive on-time architecture. This combination builds modern low-duty-ratio and ultra-fast load-step-response DC-DC converters in an ideal fashion. The output voltage ranges from 0.6 V to 5.5 V. The conversion input voltage ranges from 1.5 V to 22 V and the VDD input voltage ranges from 4.5 V to 25 V. The D-CAP3 mode uses emulated current information to control the modulation. An advantage of this control scheme is that it does not require a phase-compensation network outside which makes the device easy-to-use and also allows low-external component count. Adaptive on-time control tracks the preset switching frequency over a wide range of input and output voltage while increasing switching frequency as needed during load-step transient.

# **Frequency Selection**

TPS53515 allows users to select the switching frequency by using the RF pin. Table 1 lists the divider ratio and some example resistor values for the switching frequency selection. The 1% tolerance resistors with a typical temperature coefficient of ±100 ppm/°C are recommended. If the design requires a tighter noise margin for more reliable SW-frequency detection, use higher performance resistors.

| SWITCHING                             | RESISTOR                                           | EXAMPLE RF FREQUENCY COMBINATIONS |                        |  |  |  |

|---------------------------------------|----------------------------------------------------|-----------------------------------|------------------------|--|--|--|

| FREQUENCY<br>(f <sub>SW</sub> ) (kHz) | DIVIDER RATIO <sup>(1)</sup><br>(R <sub>DR</sub> ) | R <sub>RF_H</sub> (kΩ)            | R <sub>RF_L</sub> (kΩ) |  |  |  |

| 1000                                  | > 0.557                                            | 1                                 | 300                    |  |  |  |

| 850                                   | 0.461                                              | 180                               | 154                    |  |  |  |

| 750                                   | 0.375                                              | 200                               | 120                    |  |  |  |

| 600                                   | 0.297                                              | 249                               | 105                    |  |  |  |

| 500                                   | 0.229                                              | 240                               | 71.5                   |  |  |  |

| 400                                   | 0.16                                               | 249                               | 47.5                   |  |  |  |

| 300                                   | 0.096                                              | 255                               | 27                     |  |  |  |

| 250                                   | < 0.041                                            | 270                               | 11.5                   |  |  |  |

#### **Table 1. Switching Frequency Selection**

(1) Resistor divider ratio (R<sub>DR</sub>) is described in Equation 1.

$$R_{DR} = \frac{R_{RF\_L}}{\left(R_{RF\_L} + R_{RF\_H}\right)}$$

where

- R<sub>RF L</sub> is the low-side resistance of the RF pin resistor divider

- R<sub>RF\_H</sub> is the high-side resistance of the RF pin resistor divider

(1)

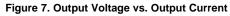

# **D-CAP3 Control and Mode Selection**

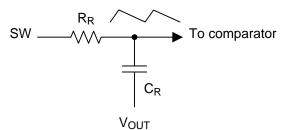

### Figure 33. Internal RAMP Generation Circuit

The TPS53515 uses D-CAP3 mode control to achieve fast load transient while maintaining the ease-of-use feature. An internal RAMP is generated and fed to the VFB pin to reduce jitter and maintain stability. The amplitude of the ramp is determined by the R-C time-constant as shown in Figure 33. At different switching frequencies, ( $f_{SW}$ ) the R-C time-constant varies to maintain relatively constant RAMP amplitude.

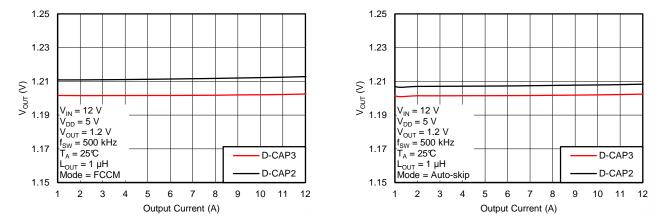

Select a MODE pin configuration as shown in Table 2 to double the R-C time-constant option. The MODE pin also selects Skip-mode or FCCM-mode operation.

### D-CAP3 Mode

From small-signal loop analysis, a buck converter using the D-CAP3 mode control architecture can be simplified as shown in Figure 34.

The D-CAP3 control architecture in TPS53515 includes an internal ripple generation network enabling the use of very low-ESR output capacitors such as multi-layer ceramic capacitors (MLCC). No external current sensing networks or compensators are required with D-CAP3 control architecture in order to simplify the power supply design. The role of the internal ripple generation network is to emulate the ripple component of the inductor current information and then combine it with the voltage feedback signal. The 0-dB frequency of the D-CAP3 architecture can be approximated as shown in Equation 2.

$$f_{0} = \frac{R_{C1} \times C_{C1} \times 0.6 \times (0.67 + D)}{2\pi \times G \times L_{X} \times C_{OUT} \times V_{OUT}}$$

where

- G is gain of the amplifier which amplifies the ripple current information generated by the network

- D is the duty ratio

(2)

The typical G value is 0.25. The  $R_{C1}C_{C1}$  time constant value varies according to the selected switching frequency as shown in Table 2

In order to secure enough phase margin, consider that  $f_0$  should be lower than 1/3 of the switching frequency, but is also higher than 5 times the  $f_{C2}$  as shown in Equation 3.

$$5 \times f_{C2} \le f_0 \le \frac{f_{SW}}{3}$$

where

$f_{C2}$  is determined by the internal network of  $R_{C2}$  and  $C_{C2}$  (2.7 kHz typ)

(3)

This example describes a DC-DC converter with an input voltage range of 12-V and an output voltage of 1.2-V. If the switching frequency is 500 kHz and the inductor is given as 1 uH, then  $C_{OUT}$  should be larger than 80  $\mu$ F, and also be smaller than 1.7 mF based on the design requirements. The characteristics of the capacitors should be also taken into considerations. For MLCC, use X5R or better dielectric and take into account derating of the capacitance by both DC bias and AC bias. When derating by DC bias and AC bias are 80% and 50%, respectively, the effective derating is 40% because 0.8 x 0.5 = 0.4. The capacitance of specialty polymer capacitors may change depending on the operating frequency. Consult capacitor manufacturers for specific characteristics.

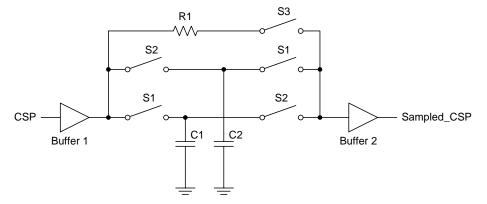

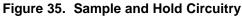

# Sample and Hold Circuitry

The sample and hold circuitry is the difference between D-CAP3 and D-CAP2. The sample and hold circuitry, which is a advance control scheme to boost output voltage accuracy higher on the TPS53515, is one of features of the TPS53515. The sample and hold circuitry generates a new DC voltage of CSN instead of the voltage which is produced by  $R_{C2}$  and  $C_{C2}$  which allows for tight output-voltage accuracy and makes the TPS53515 more competitive.

ZHCSBL7 -AUGUST 2013

TPS53515

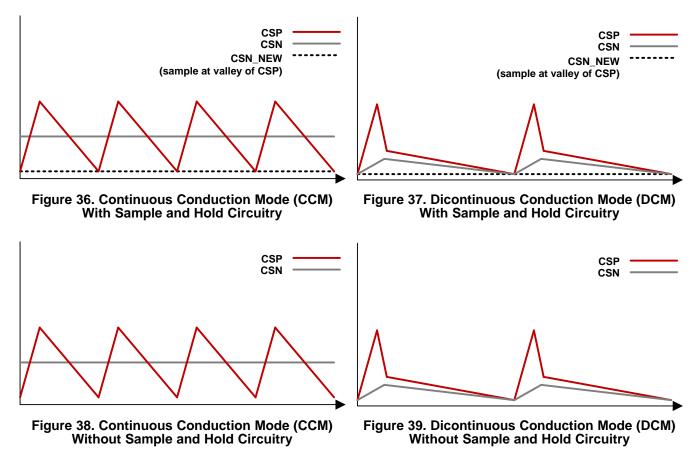

Figure 40. Output Voltage vs Output Current

| MODE<br>SELECTION   | ACTION           | R <sub>MODE</sub><br>(kΩ) | R-C TIME<br>CONSTANT (μs) | FRE | VITCHI<br>QUEN<br><sub>SW</sub> (kH: | CIES |  |  |

|---------------------|------------------|---------------------------|---------------------------|-----|--------------------------------------|------|--|--|

|                     |                  |                           | 60                        | 250 | and                                  | 300  |  |  |

|                     |                  | 0                         | 50                        | 400 | and                                  | 500  |  |  |

| Skip Mode           |                  | 0                         | 40                        | 600 | and                                  | 750  |  |  |

|                     | Pull down to GND |                           | 30                        | 850 | and                                  | 1000 |  |  |

|                     | Full down to GND |                           | 120                       | 250 | and                                  | 300  |  |  |

|                     |                  | 150                       | 100 400                   |     |                                      |      |  |  |

|                     |                  | 150                       | 80                        | 600 | and                                  | 750  |  |  |

|                     |                  |                           | 60                        | 850 | and                                  | 1000 |  |  |

|                     |                  |                           | 60                        | 250 | and                                  | 300  |  |  |

|                     |                  | 20                        | 50                        | 400 | and                                  | 500  |  |  |

|                     |                  | 20                        | 40                        | 600 | and                                  | 750  |  |  |

| FCCM <sup>(1)</sup> | Connect to       |                           | 30                        | 850 | and                                  | 1000 |  |  |

| FCCIWI V            | PGOOD            |                           | 250                       | and | 300                                  |      |  |  |

|                     |                  | 150                       | 100                       | 400 | and                                  | 500  |  |  |

|                     |                  | 150                       | 80                        | 600 | and                                  | 750  |  |  |

|                     |                  |                           | 60                        | 850 | and                                  | 1000 |  |  |

|                     |                  |                           | 120                       | 250 | and                                  | 300  |  |  |

| ECOM                | Connect to VREG  | 0                         | 100                       | 400 | and                                  | 500  |  |  |

| FCCM                | Connect to VREG  | U                         | 80                        | 600 | and                                  | 750  |  |  |

|                     |                  |                           | 60                        | 850 | and                                  | 1000 |  |  |

Table 2. Mode Selection and Internal RAMP RC Time Constant

(1) Device goes into Forced CCM (FCCM) after PGOOD becomes high.

# Auto-Skip Eco-mode™ Light Load Operation

While the MODE pin is pulled to GND directly or via 150-k $\Omega$  resistor, the TPS53515 automatically reduces the switching frequency at light-load conditions to maintain high efficiency. This section describes the operation in detail.

### ZHCSBL7 -AUGUST 2013

www.ti.com.cn

(4)

**ISTRUMENTS**

FXAS

As the output current decreases from heavy load condition, the inductor current also decreases until the rippled valley of the inductor current touches zero level. Zero level is the boundary between the continuous-conduction and discontinuous-conduction modes. The synchronous MOSFET turns off when this zero inductor current is detected. As the load current decreases further, the converter runs into discontinuous-conduction mode (DCM). The on-time is maintained to a level approximately the same as during continuous-conduction mode operation so that discharging the output capacitor with a smaller load current to the level of the reference voltage requires more time. The transition point to the light-load operation  $I_{O(LL)}$  (for example: the threshold between continuous-and discontinuous-conduction mode) is calculated as shown in Equation 4.

$$I_{OUT(LL)} = \frac{1}{2 \times L \times f_{SW}} \times \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

where

• f<sub>SW</sub> is the PWM switching frequency

Using only ceramic capacitors is recommended for Auto-skip mode.

### Adaptive Zero-Crossing

The TPS53515 uses an adaptive zero-crossing circuit to perform optimization of the zero inductor-current detection during skip-mode operation. This function allows ideal low-side MOSFET turn-off timing. The function also compensates the inherent offset voltage of the Z-C comparator and delay time of the Z-C detection circuit. Adaptive zero-crossing prevents SW-node swing-up caused by too-late detection and minimizes diode conduction period caused by too-early detection. As a result, the device delivers better light-load efficiency.

### Forced Continuous-Conduction Mode

When the MODE pin is tied to the PGOOD pin through a resistor, the controller operates in continuous conduction mode (CCM) during light-load conditions. During CCM, the switching frequency maintained to an amost constant level over the entire load range which is suitable for applications requiring tight control of the switching frequency at the cost of lower efficiency.

# **Power-Good**

The TPS53515 has power-good output that indicates high when switcher output is within the target. The powergood function is activated after the soft-start operation is complete. If the output voltage becomes within  $\pm 8\%$  of the target value, internal comparators detect the power-good state and the power-good signal becomes high after a 1-ms internal delay. If the output voltage goes outside of  $\pm 16\%$  of the target value, the power-good signal becomes low after a 2-µs internal delay. The power-good output is an open-drain output and must be pulled-up externally.

# **Current Sense and Overcurrent Protection**

The TPS53515 has cycle-by-cycle overcurrent limiting control. The inductor current is monitored during the OFF state and the controller maintains the OFF state during the period that the inductor current is larger than the overcurrent trip level. In order to provide good accuracy and a cost-effective solution, the TPS53515 supports temperature compensated MOSFET  $R_{DS(on)}$  sensing. Connect the TRIP pin to GND through the trip-voltage setting resistor,  $R_{TRIP}$ . The TRIP terminal sources  $I_{TRIP}$  current, which is 10 µA typically at room temperature, and the trip level is set to the OCL trip voltage  $V_{TRIP}$  as shown in Equation 5.

$$V_{\text{TRIP}} = R_{\text{TRIP}} \times I_{\text{TRIP}}$$

where

- $V_{TRIP}$  is in mV

- $R_{TRIP}$  is in k $\Omega$

- I<sub>TRIP</sub> is in μA

(5)

The inductor current is monitored by the voltage between the GND pin and SW pin so that the SW pin is properly connected to the drain terminal of the low-side MOSFET.  $I_{TRIP}$  has a 3000-ppm/°C temperature slope to compensate the temperature dependency of  $R_{DS(on)}$ . The GND pin acts as the positive current-sensing node. Connect the GND pin to the proper current sensing device, (for example, the source terminal of the low-side MOSFET.)

Because the comparison occurs during the OFF state,  $V_{TRIP}$  sets the valley level of the inductor current. Thus, the load current at the overcurrent threshold,  $I_{OCP}$ , is calculated as shown in Equation 6.

$$I_{OCP} = \frac{V_{TRIP}}{\left(\!8 \times R_{DS(on)}\right)} + \frac{I_{IND(ripple)}}{2} = \frac{V_{TRIP}}{\left(\!8 \times R_{DS(on)}\right)} + \frac{1}{2 \times L \times f_{SW}} \times \frac{\left(V_{IN} - V_{OUT}\right) \times V_{OUT}}{V_{IN}}$$

where

- R<sub>DS(on)</sub> is the on-resistance of the low-side MOSFET

- R<sub>TRIP</sub> is in kΩ

(6)

In an overcurrent condition, the current to the load exceeds the current to the output capacitor thus the output voltage tends to decrease. Eventually, the output voltage crosses the undervoltage-protection threshold and shuts down.

A special trimming option uses hiccup mode as the overcurrent protection (OCP).

### **Overvoltage and Undervoltage Protection**

The TPS53515 monitors a resistor-divided feedback voltage to detect overvoltage and undervoltage. When the feedback voltage becomes lower than 68% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins counting. After 1 ms, the TPS53515 latches OFF both high-side and low-side MOSFETs drivers. The UVP function enables after soft-start is complete.

When the feedback voltage becomes higher than 120% of the target voltage, the OVP comparator output goes high and the circuit latches OFF the high-side MOSFET driver and turns on the low-side MOSFET until reaching a negative current limit. Upon reaching the negative current limit, the low-side FET is turned off and the high-side FET is turned on again for a minimum on-time. The TPS53515 operates in this cycle until the output voltage is pulled down under the UVP threshold voltage for 1 ms. After the 1-ms UVP delay time, the high-side FET is latched off and low-side FET is latched on. The fault is cleared with a reset of VDD or by re-toggling EN pin.

# Out-Of-Bounds Operation (OOB)

The TPS53515 has an out-of-bounds (OOB) overvoltage protection that protects the output load at a much lower overvoltage threshold of 8% above the target voltage. OOB protection does not trigger an overvoltage fault, so the device is not latched off after an OOB event. OOB protection operates as an early no-fault overvoltage-protection mechanism. During the OOB operation, the controller operates in forced PWM mode only by turning on the low-side FET. Turning on the low-side FET beyond the zero inductor current quickly discharges the output capacitor thus causing the output voltage to fall quickly towards the setpoint. During the operation, the cycle-by-cycle negative current limit is also activated to ensure the safe operation of the internal FETs.

# **UVLO Protection**

The TPS53515 monitors the voltage on the VDD pin. If the VDD pin voltage is lower than the UVLO off-threshold voltage, the switch mode power supply shuts off. If the VDD voltage increases beyond the UVLO on-threshold voltage, the controller turns back on. UVLO is a non-latch protection.

### Thermal Shutdown

The TPS53515 monitors internal temperature. If the temperature exceeds the threshold value (typically 140°C), TPS53515 shuts off. When the temperature falls approximately 40°C below the threshold value, the device turns on. Thermal shutdown is a non-latch protection.

### ZHCSBL7 -AUGUST 2013

# **External Parts Selection**

The external components selection is a simple process using D-CAP3<sup>™</sup> Mode. Select the external components using the following steps

### 1. CHOOSE THE SW FREQUENCY

The SW frequency is configured by the resistor divider on the RF pin. Select one of eight SW frequencies from 250 kHz to 1 MHz. Refer Table 1 for the relationship between the SW frequency and resistor-divider configuration.

# 2. CHOOSE THE OPERATION MODE

Select the operation mode using Table 2.

### 3. CHOOSE THE INDUCTOR

Determine the inductance value to set the ripple current at approximately 1/4 to 1/2 of the maximum output current. Larger ripple current increases output ripple voltage, improves S/N ratio, and helps stable operation.

$$L = \frac{1}{I_{IND(ripple)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}} = \frac{3}{I_{OUT(max)} \times f_{SW}} \times \frac{\left(V_{IN(max)} - V_{OUT}\right) \times V_{OUT}}{V_{IN(max)}}$$

(7)

The inductor requires a low DCR to achieve good efficiency. The inductor also requires enough room above peak inductor current before saturation. The peak inductor current is estimated using Equation 8.

$$I_{\text{IND}(\text{peak})} = \frac{V_{\text{TRIP}}}{8 \times R_{\text{DS}(\text{on})}} + \frac{1}{L \times f_{\text{SW}}} \times \frac{\left(V_{\text{IN}(\text{max})} - V_{\text{OUT}}\right) \times V_{\text{OUT}}}{V_{\text{IN}(\text{max})}}$$

(8)

# 4. CHOOSE THE OUTPUT CAPACITOR

The output capacitor selection is determined by output ripple and transient requirement. When operating in CCM, the output ripple has two components as shown in Equation 9. Equation 10 and Equation 11 define these components.

$$V_{\text{RIPPLE}} = V_{\text{RIPPLE}(C)} + V_{\text{RIPPLE}(\text{ESR})}$$

(9)

$$V_{RIPPLE(C)} = \frac{I_{L(ripple)}}{8 \times C_{OUT} \times f_{SW}}$$

(10)

$$V_{RIPPLE(ESR)} = I_{L(ripple)} \times ESR$$

(11)

VRIPPLE(ESR) = <sup>I</sup>L(ripple) × LSR

5. DETERMINE THE VALUE OF R1 AND R2

The output voltage is programmed by the voltage-divider resistors, R1 and R2, shown in Figure 1. R1 is connected between the VFB pin and the output, and R2 is connected between the VFB pin and GND. The recommended R2 value is from 1 k $\Omega$  to 20 k $\Omega$ . Determine R1 using Equation 12.

$$R1 = \frac{V_{OUT} - 0.6}{0.6} \times R2$$

(12)

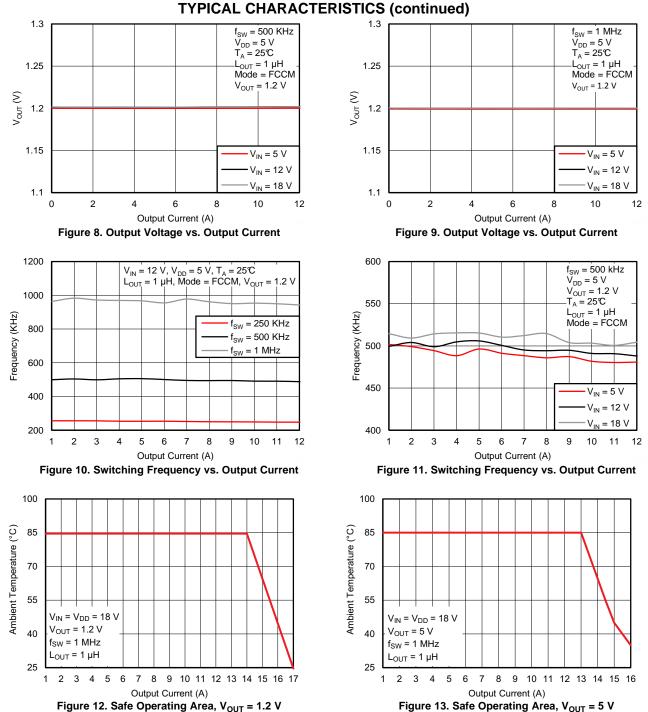

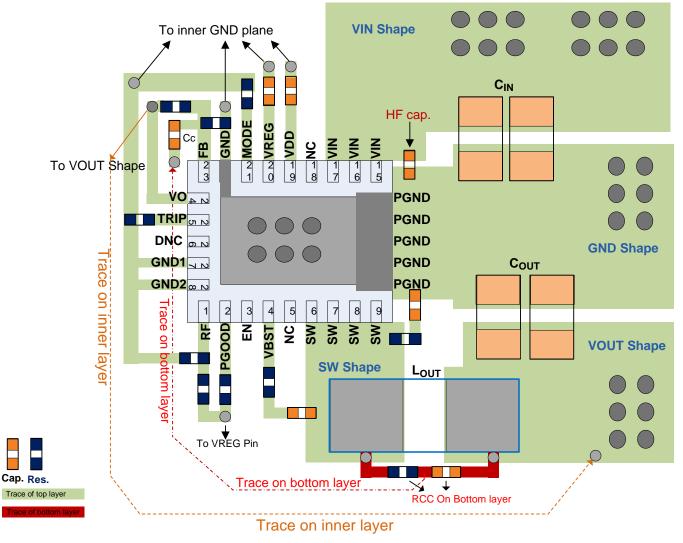

# LAYOUT CONSIDERATIONS

Before beginning a design using the TPS53515, consider the following:

- Place the power components (including input and output capacitors, the inductor, and the TPS53515) on the solder side of the PCB. In order to shield and isolate the small signal traces from noisy power lines, insert and connect at least one inner plane to ground.

- All sensitive analog traces and components such as VFB, PGOOD, TRIP, MODE, and RF must be placed away from high-voltage switching nodes such as SW and VBST to avoid coupling. Use internal layers as ground planes and shield the feedback trace from power traces and components.

- Pin 22 (GND pin) must be connected directly to the thermal pad. Connect the thermal pad to the PGND pins and then to the GND plane.

- Place the VIN decoupling capacitors as close to the VIN and PGND pins as possible to minimize the input AC-current loop.

- Place the feedback resistor near the IC to minimize the VFB trace distance.

- Place the frequency-setting resistor (RF), OCP-setting resistor (R<sub>TRIP</sub>) and mode-setting resistor (R<sub>MODE</sub>) close to the device. Use the common GND via to connect the resistors to the GND plane if applicable.

- Place the VDD and VREG decoupling capacitors as close to the device as possible. Provide GND vias for each decoupling capacitor and ensure the loop is as small as possible.

- The PCB trace is defined as switch node, which connects the SW pins and high-voltage side of the inductor. The switch node should be as short and wide as possible.

- Use separated vias or trace to connect SW node to the snubber, bootstrap capacitor, and ripple-injection resistor. Do not combine these connections.

- Place one more small capacitor (2.2 nF- 0402 size) between the VIN and PGND pins. This capacitor must be placed as close to the IC as possible.

- TI recommends placing a snubber between the SW shape and GND shape for effective ringing reduction. The value of snubber design starts at 3  $\Omega$  + 470 pF.

- Consider R,C,Cc network (Ripple injection network) component placement and place the AC coupling capacitor, Cc, close to the device, and R and C close to the power stage.

- See Figure 42 for the layout recommendation.

Figure 42. Layout Recommendation

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)        | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                        | (6)                           |                      | 40.4.05      | TD050515                |         |

| TPS53515RVER     | ACTIVE        | VQFN-CLIP    | RVE                | 28   | 3000           | RoHS-Exempt<br>& Green | NIPDAU   SN                   | Level-2-260C-1 YEAR  | -40 to 85    | TPS53515                | Samples |

| TPS53515RVET     | ACTIVE        | VQFN-CLIP    | RVE                | 28   | 250            | RoHS-Exempt<br>& Green | NIPDAU   SN                   | Level-2-260C-1 YEAR  | -40 to 85    | TPS53515                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# **MECHANICAL DATA**

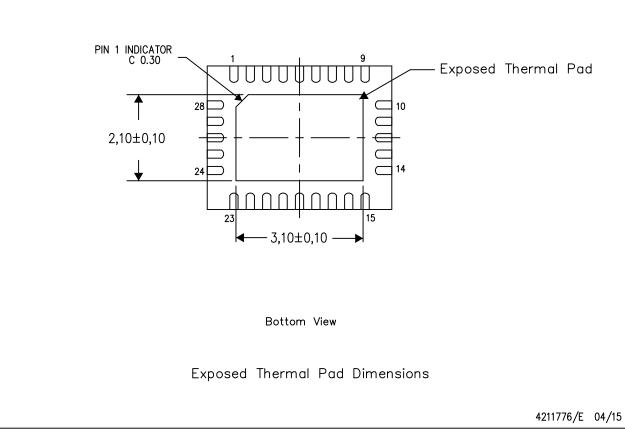

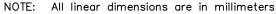

- C. Quad Flatpack, No-leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions. E. Falls within JEDEC MO-220.

# RVE (R-PVQFN-N28)

# PLASTIC QUAD FLATPACK NO-LEAD

### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Electroformed stencils offer adequate release at thicker values/lower Area Ratios. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- E. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### 重要声明和免责声明

Ⅱ 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任:(1)针对您的应用选择合适的TI产品;(2)设计、 验证并测试您的应用;(3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用 所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权 许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI所提供产品均受TI的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址:上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司